# Fabrication and Characterization of (100) Silicon Membranes for a **Multi-beam Superconducting Heterodyne Receiver**

Shohei Ezaki, Shan Wenlei, Matthias Kroug, Takafumi Kojima, Alvaro Gonzalez, Shin'ichiro Asayama and Takashi Nogchi

National Astronomical Observatory of Japan, Mitaka, Tokyo, Japan E-mail: shohei.ezaki@nao.ac.jp

### Introduction

Narrow field of view (FOV) is one of the significant limitations of a radio telescope for large area surveys. Aiming to extend the FOV of the radio telescopes, we started to develop the multi-beam superconducting heterodyne receiver which is highly compact and can accommodate more pixels than before. The concept for the multi-beam superconducting heterodyne receiver is implementing planar orthomode transducers (OMTs) and superconductor-insulator-superconductor circuits into an integrated circuit (IC). The fabrication of membranes is one of the most important techniques for these ICs, because the planar OMTs and wave probes that couples local oscillator power in the IC are fabricated on the membranes. As a pre-study before the IC fabrication, we fabricated (100) silicon membranes of 3 mm in diameter on the surface of silicon on insulator substrates, and the characteristics of the membranes were investigated.

**17<sup>th</sup> International Workshop** on Low Temperature detector **PC-12**

### **Experimental Results**

## Summary

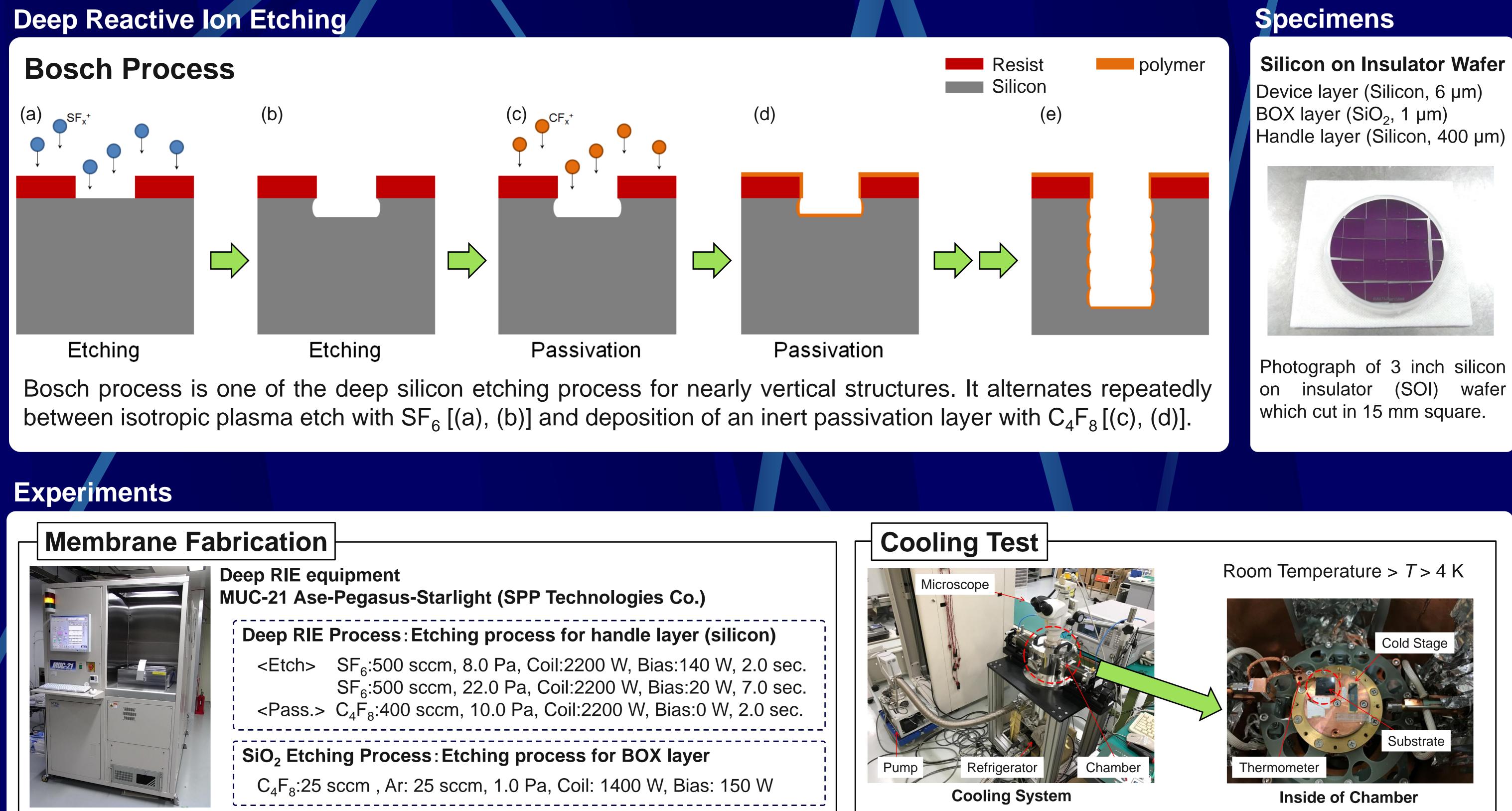

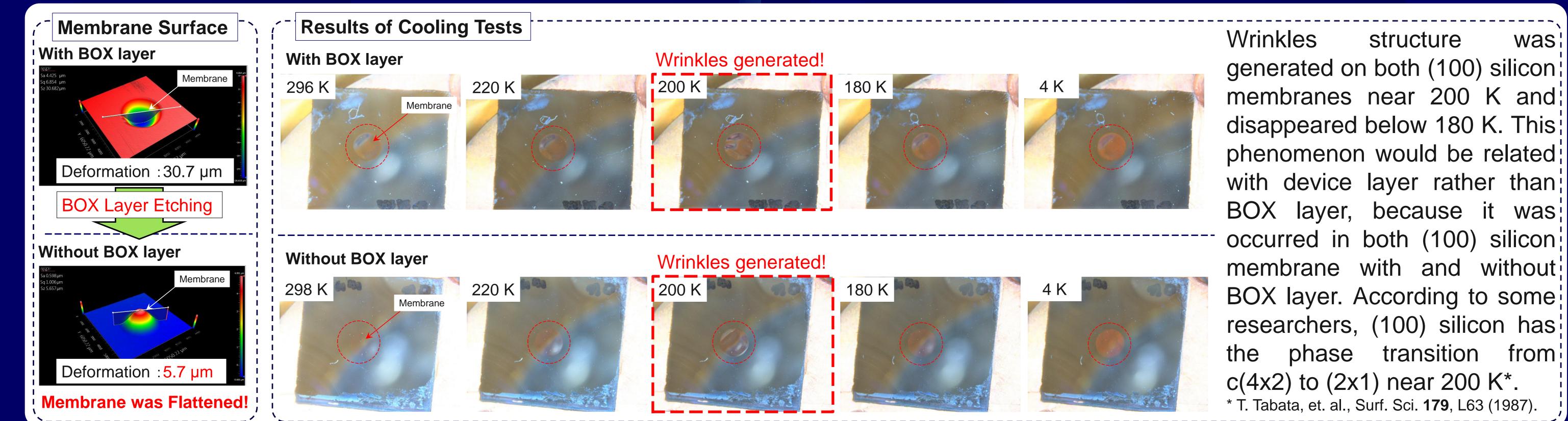

We fabricated the membranes 3 mm in diameter on the SOI substrates using Deep RIE equipment. The handle layer of one SOI substrate was etched using Bosch process with the BOX layer remained. The BOX layer of the other SOI substrate was removed using  $C_4F_8$  based plasma etching after the handle layer etching. The (100) silicon membranes with the BOX layer and without the BOX layer have the ark-like deformation with maximum height of 30.7 µm and 5.7 µm, respectively. It shows the (100) silicon membranes of SOI substrates are effectively flattened by etching the BOX layers under the (100) silicon device layers. Both (100) silicon membranes were cooled from room temperature to 4 K by the GM refrigerator. Wrinkles structure was generated on both (100) silicon membrane near 200 K. However the wrinkles structure of the (100) silicon membrane was disappeared below about 180 K.